Abrimos el Navegador de proyectos del Xilinx Ise 10.1:

Damos OK en la ventana Did you Know y cierre la ventana What's New in Xilinx Ise Design suite 10.1.

Esas ventanas ofrecen información interesante sobre el manejo del software, por lo cual antes de cerrarlas es conveniente leer dicha información.

Seleccione: file --> New proyect. Indique la carpeta en la que va a trabajar y elija como Esquemático

( Schematic) el tipo de diseño que se va a realizar.

Al dar Siguiente en la nueva ventana debe colocar los nombre de la familia, dispositivo,empaque, velocidad, herramienta de síntesis, Simulador, lenguaje de preferencia para efectuar la simulación, etc, tal como se muestra en la siguiente gráfica:

De siguiente a las nuevas ventanas y finalmente las propiedades del proyecto aparecen resumidas en la última de ellas.

Luego de doble Click en Create New Source y elija Schematic, y vuelva a asignar como compuertas el nombre del archivo esquemático. No importa que el nombre del proyecto y del archivo esquemático sea el mismo.

Al dar siguiente y luego finalizar en los cuadros de diálogo restantes se abrirá el editor de esquemáticos para dibujar las compuertas lógicas.

En la parte izquierda dar click en la etiqueta Symbols y seleccionar en categories: logic.

En una forma muy similar a como se trabaja el ISPLEVER de Lattice Semiconductor se dibuja el esquemático con sus entradas y salidas:

Se salva el esquemático.

En Project > New Source abrimos una nueva caja de diálogos para crear un nuevo archivo que llamamos comp_tb para el banco de pruebas Test Bench Waveform:

Damos NEXT dos veces y luego al finalizar este proceso, se abre una nueva caja de diálogos tal como se muestra a continuación:

En Clock Information seleccionamos como "Combinatorial" nuestro diseño.Lo demás campos los dejamos igual.

Luego se cambia por una nueva ventana así:

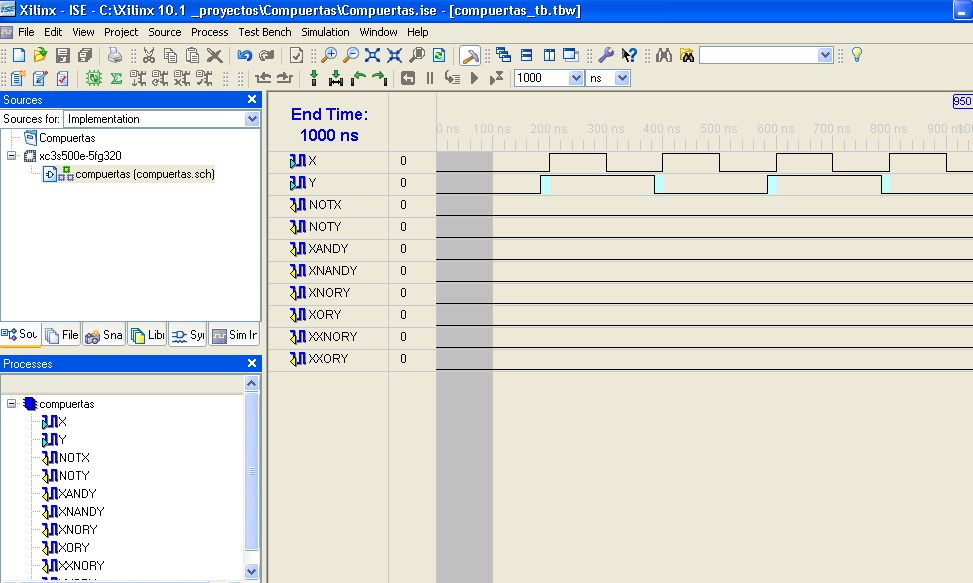

Pulsamos Finish para abrir el editor de formas de onda, para dibujar diferentes combinaciones de valores en las entradas X y Y

En la parte superior izquierda de la pantalla en la ventana Sources seleccione Behavioral Simulation.

Luego, en la parte inferior izquierda de la pantalla, en Process se despliega el menú Xlinx Ise Simulator y de doble Click en Behavioral Model.

Luego se cambia por una nueva ventana así:

Pulsamos Finish para abrir el editor de formas de onda, para dibujar diferentes combinaciones de valores en las entradas X y Y

En la parte superior izquierda de la pantalla en la ventana Sources seleccione Behavioral Simulation.

Luego, en la parte inferior izquierda de la pantalla, en Process se despliega el menú Xlinx Ise Simulator y de doble Click en Behavioral Model.

Al ejecutarse la simulación debemos comprobar que el resultado es el esperado.

Luego de haber efectuado la simulación se hace la asignación de pines en la tarjeta Spartan 3E ; para ello en Source seleccionamos implementación y en Process: User Constraints.

Al dar (+) en User Constraints damos doble click en asignación de pines post-síntesis:

Después de haberse realizado la síntesis del esquemático se abre una ventana que permite la asignación de pines:

A medida que se va localizando cada entrada y salida como pines en la tarjeta se va señalizando con azul en la gráfica de la derecha el pin asignado.

Las entradas las ubicamos en los pines L14 y L13 de los interruptores de la tarjeta:

Para los pines en las salidas se tiene en cuenta los 8 leds de que dispone la tarjeta que se encuentran ubicados en la parte duperior de los interruptores:

Al asignar los pines, se crea un archivo denominado: compuertas.ucf

Al observar el resumen del diseño ( View Design Summary) en pin report dando click en la columna Signal Name se puede verificar que los pines se asignaron en forma correcta y procedemos a dar doble Click en Configure target Device para generar el archivo de programación Generate Programming file.

Aparece una advertencia y damos YES en la ventana respectiva. Debe estar alimentada la tarjeta y conectado el cable USB al computador para que se efectúe la detección automática de dicho cable y se pueda efectuar la respectiva programación de la FPGA dando Click en RUN (botón derecho) sobre la FPGA y omitiendo los otros 2 dispositivos, el CPLD y la memoria PROM.

Al efectuarse la programación exitosamente aparece un mensaje alusivo en color Azul así:

Al accionar los interruptores se puede observar en los leds el correcto manejo de las compuertas.

Luego de haber efectuado la simulación se hace la asignación de pines en la tarjeta Spartan 3E ; para ello en Source seleccionamos implementación y en Process: User Constraints.

Al dar (+) en User Constraints damos doble click en asignación de pines post-síntesis:

Después de haberse realizado la síntesis del esquemático se abre una ventana que permite la asignación de pines:

A medida que se va localizando cada entrada y salida como pines en la tarjeta se va señalizando con azul en la gráfica de la derecha el pin asignado.

Las entradas las ubicamos en los pines L14 y L13 de los interruptores de la tarjeta:

Para los pines en las salidas se tiene en cuenta los 8 leds de que dispone la tarjeta que se encuentran ubicados en la parte duperior de los interruptores:

Al asignar los pines, se crea un archivo denominado: compuertas.ucf

Al observar el resumen del diseño ( View Design Summary) en pin report dando click en la columna Signal Name se puede verificar que los pines se asignaron en forma correcta y procedemos a dar doble Click en Configure target Device para generar el archivo de programación Generate Programming file.

Aparece una advertencia y damos YES en la ventana respectiva. Debe estar alimentada la tarjeta y conectado el cable USB al computador para que se efectúe la detección automática de dicho cable y se pueda efectuar la respectiva programación de la FPGA dando Click en RUN (botón derecho) sobre la FPGA y omitiendo los otros 2 dispositivos, el CPLD y la memoria PROM.

Al efectuarse la programación exitosamente aparece un mensaje alusivo en color Azul así:

Al accionar los interruptores se puede observar en los leds el correcto manejo de las compuertas.

.jpg)

.jpg)

.jpg)

.jpg)