La tarjeta BASYS 2 es una tarjeta de desarrollo,fabricada por la compañía DIGILENT, que contiene una FPGA Xilinx Spartan 3E-100,XC3S100E-CP132, un arreglo lógico programable de campo con 100.000 compuertas.

Está diseñada para el aprendizaje de sistemas digitales de complejidad media utilizando un entorno de desarrollo profesional. Es la ideal para el estudio de Digitales 2 a nivel de Ingeniería Electrónica y Biomédica en la UAN.

Además de la FPGA, esta tarjeta contiene una serie de recursos que pueden ser utilizados en los diseños de los circuitos. Concretamente contiene:

• 4 pulsadores.

• 8 interruptores deslizables.

• 8 LEDS, cátodo común.

• 4 displays de 7 segmentos en visualización dinámica.

• Un conector de teclado de PC (PS2)

• Una salida VGA para monitor de computador.

Todos estos recursos se encuentran conectados a las patillas de la FPGA de la forma que se indica en la siguiente figura:

Observe que cada elemento se identifica con una Letra y un Número de uno o dos dígitos, con el cual se identifica el Pin, por ejemplo el LD0 se localiza como M5, el Switche SW0 está asociado con el pin P11, etc.

Además la FPGA posee una entrada conectada a un reloj de 50 MHz que corresponde a la localización de pin B8.

Se entiende que para el conector de teclado o el monitor VGA del computador tambien hay pines asociados que por el momento no se requieren, debido al uso inicial que se pretende dar a la tarjeta en las primeras prácticas, solo utilizando Switches y pulsadores como Entradas y los Leds y Displays de 7 segmentos en las salidas de los circuitos a implementar. Mas adelante se puede utilizar el Teclado para introducir datos, y el Monitor del PC para visualizar la salida.

Adicionalmente existen 4 conectores para trabajar externamente entradas y salidas, por ejemplo con el protoboard. Los cuatro conectores de expansión estándar permiten a la tarjeta Basys2 crecer utilizando circuitos diseñados por el usuario o PMods. (Los PMods son módulos de E/S analógicos y digitales de bajo costo que ofrecen conversión A/D y D/A, drivers para motor, entradas de sensor y muchas otras características).

Supongamos que por ejemplo se desea trabajar con 4 leds de alto brillo o leds de chorro. Digilent ofrece por 10 dólares un módulo de expansión de 6 pines con los leds y sus transistores para que los manejen.

Veamos el diagrama lógico de los leds y transistores:

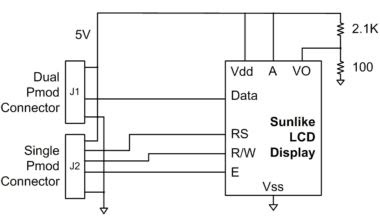

Si necesitamos un display de cristal líquido LCD, por 35 dólares Digilent ofrece la respectiva tarjeta expansora que utiliza dos puertos, o sea 6 pines:

Veamos su diagrama eléctrico:

Se ofrece adicionalmente documentos de soporte para cada módulo expansor.

El lector puede conocer todos los módulos de expansión disponibles con sus respectivos precios en

https://www.digilentinc.com/Products/Catalog.cfm?NavPath=2,401&Cat=9

Uno de los 6 pines del conector es tierra (GND) y otro es Vcc de 3,3

voltios en cada puerto de expansión.

.

Se pueden observar en el gráfico anterior las resistencias de protección contra corto circuitos a las salidas, lo mismo que Diodos de protección ESD a tierra contra descargas electrostáticas.

Las descargas

electrostáticas, como su nombre lo indica, consisten en un flujo

repentino de corriente a través de un material, que generalmente es un

aislante, pero que la diferencia de potencial entre sus extremos genera

un campo eléctrico de cierta magnitud, convirtiendo los átomos del

material en iones que conducen corriente.

Estas descargas se

convierten en una seria amenaza para algunos dispositivos electrónicos

sensibles, ya que gran parte de ellos incorporan una capa delgada de

aislante, como por ejemplo dióxido de silicio, la cual se rompe cuando

es sometida a altos voltajes, dañando irreparablemente el dispositivo.

Síntesis de circuitos mediante la tarjeta BASYS 2:

La síntesis de circuitos se puede realizar por medio del editor esquemático o mediante el lenguaje de descripción hardware VHDL. Se compilará utilizando el entorno ISE de XILINX como el XILINX ISE 10.1 que está disponible en el laboratorio de Simulación de Electrónica-Biomédica en la UAN,sede Sur,Bogotá. Este entorno es capaz de crear un archivo para la configuración de la FPGA a partir del código VHDL que se escribe(archivo de “bit stream” con extensión .bit). Dicho archivo debe ser cargado en la tarjeta BASYS 2. Esto hace que el hardware interno de la FPGA se configure para seguir las especificaciones de lo que se requiere implementar.

Para volcar el contenido del archivo en la FPGA y configurarla es necesario utilizar el programa ADEPT de DIGILENT, el cual también debe estar disponible en el PC adicional al XILINX ISE.

Para implementar un circuito digital en la FPGA de la tarjeta Digilent Basys 2 deben seguirse los siguientes pasos:

1). Dibujar el circuito lógico en el Editor Esquemático o escribir un código en VHDL que describa el hardware que queremos sintetizar.

2). Compilar el esquemático o el código VHDL y generar el archivo de “bit stream”. Evidentemente el archivo no se generará si el programa tiene errores.

3) Efectuar la simulación del circuito a implementar.

4). Una vez generado el fichero de “bit stream”, deberá utilizarse el programa ADEPT para volcarlo en la FPGA.

5). En este momento, la FPGA se convierte en un circuito que deberá realizar la tarea que haya sido descrita mediante el esquemático o el código VHDL.

Utilización del entorno ISE:

Para realizar una síntesis mediante el entorno ISE debe crearse un proyecto.

Vaya al menú FILE -> NEW PROJECT. Aparecerá una ventana donde tendrá que escribir el nombre del nuevo proyecto. Asegúrese también que en la casilla de selección “Top level Source Type” aparece “HDL”.

En la siguiente pantalla deberá ajustar los siguientes valores:

Family: Spartan 3E

Device: XC3S100E

Package: CP132

Speed: -5

Synthesis tool: XST (VHDL/Verilog)

Simulator: ISim (VHDL/Verilog)

Preferred Language: VHDL

Por último sáltese las siguientes pantallas pulsando en “Next”. En la última aparecerá el botón “Finish”.

Para compilar el código y generar el “bit stream” , seleccione el fichero o archivo principal del proyecto y haga doble click en “Generate Programming File” en la parte inferior izquierda, después de haber efectuado la asignación de pines con el editor respectivo “Edit Constraints" y generar el respectivo archivo con extensión UCF.

Programación de la FPGA de la tarjeta Digilent Basys 2:

Contiene un cable USB que le proporciona energía y es utilizado como interfaz de programación, por lo que ninguna otra fuente de poder o cable de programación es requerido.

Para el uso de las tarjetas de Digilent que cuentan con conector Mini-USB como la Basys2 se requiere un software extra para poder realizar la comunicación:

Adept de Digilent; El software puede descargarse de manera gratuita en el sitio web

http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,66,828&Prod=ADEPT2, en la sección “Software”: Digilent Adept, el paquete a descargar para Windows es Adept 2.6.1 System, 32/64-bit. Su instalación es muy sencilla, basta con hacer doble clic en el icono del software descargado y seguir las instrucciones.

Conecte la tarjeta Basys2 a un puerto USB disponible de una computador, Windows reconocerá que se ha conectado un nuevo dispositivo y procederá a asociarlo con el controlador adecuado. Arranque el programa: ADEPT.

y si la tarjeta se encuentra conectada adecuadamente, se debe tener algo como lo que se muestra en la figura siguiente:

Mediante el botón “Browse…” situado en la línea superior puede seleccionar el archivo que desea cargar. El archivo debe tener extensión .bit A continuación haga click en el botón “Program”.a la derecha de “Browse…” Acepte la ventana que aparece y el fichero será transferido a la FPGA configurándola de tal manera que obedezca el circuito descrito en su diseño.

Durante la programación, un led de color rojo, que se encuentra a un lado de los pines de alimentación externa de la tarjeta se enciende, una vez terminado el proceso se indica si ha sido exitoso en la ventana de mensajes de Adept.

En los Slices se realiza la mayor parte dela funcionalidad de la FPGA y suelen estar agrupados de 2 en 2 o de 4 en 4 formando los bloques lógicos configurables (CLBs). Dentro de este componente encontramos los módulos LUT, registros y multiplexores programables en un número que depende de familia de FPGA, y tal como se muestra en la siguiente figura:

En los Slices se realiza la mayor parte dela funcionalidad de la FPGA y suelen estar agrupados de 2 en 2 o de 4 en 4 formando los bloques lógicos configurables (CLBs). Dentro de este componente encontramos los módulos LUT, registros y multiplexores programables en un número que depende de familia de FPGA, y tal como se muestra en la siguiente figura:

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

ada

ada